Arm’s Broadest Ever Automotive Enhanced IP Portfolio Designed for the Future of Computing in Vehicles

The automotive industry is undergoing seismic change and transformation. Vehicles, now and in the future, are being defined by the electronic systems powering them, as they essentially become “a computer on wheels” that are the most complex technology devices people own.

This complexity is being driven by the proliferation of AI and an exponential growth of software that are defining software-defined vehicles (SDVs). This requires new levels of performance, efficiency, safety and security.

Foundational compute for the automotive market

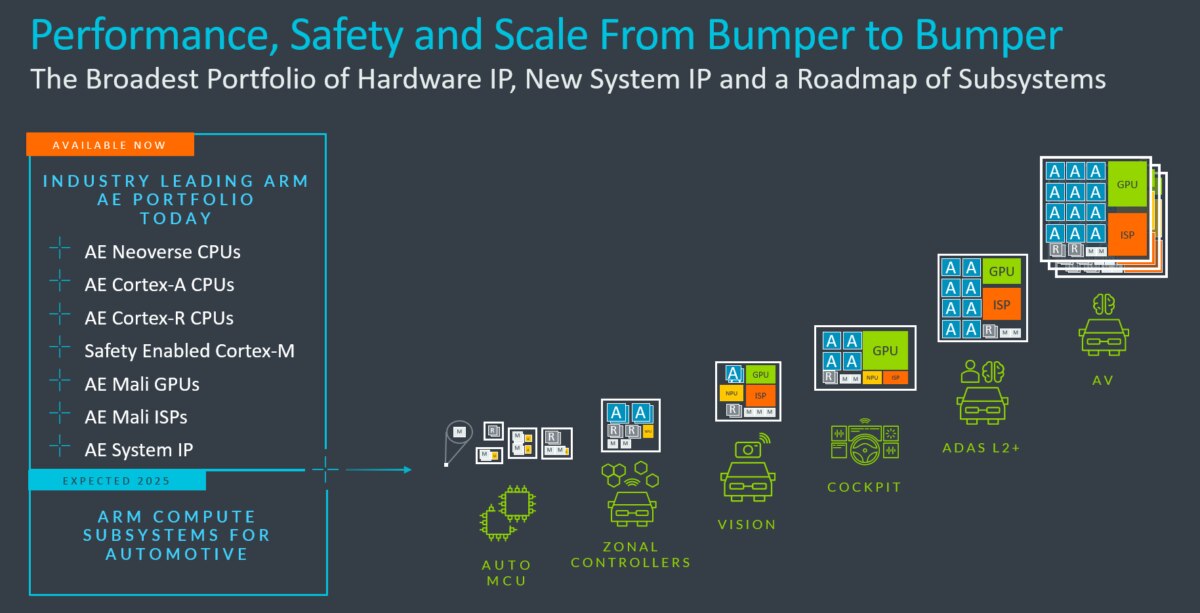

Arm is delivering new hardware and immediate software enablement from day one to meet these demands and accelerate automotive development and deployment. A vital part of this commitment is a brand-new suite of leading-edge processors that deliver AI-accelerated, purpose-built automotive compute. This expands the portfolio of Arm Automotive Enhanced “AE” IP to an unprecedented scale, while providing unrivalled performance, low power, safety, security, scalability and flexibility for automotive system-on-chip (SoC) designers worldwide.

The additions to the Arm AE IP portfolio include a brand-new server-class Neoverse CPU with features specifically designed for the automotive market, two new Armv9 A-class CPUs, a new R-class CPU and a new Image Signal Processor (ISP). The portfolio also offers key system IP, including Interconnect, Generic Interrupt Controller (GIC) and memory management unit (MMU) for a wide range of SoC solutions.

Together these products are enabling leading automotive partners, including Marvell, MediaTek, NVIDIA, NXP, Renesas, Telechips and Texas Instruments among others, to develop new classes of computing systems, technologies and devices, ranging from zonal controllers to digital cockpit and in-vehicle infotainment (IVI) systems, from advanced driver assistance systems (ADAS) to autonomous driving enabled by the ongoing AI revolution. You can read more about what our silicon partners have to say here.

In addition to the new processors, we are investing in a roadmap of Arm Compute Subsystems (CSS) for automotive designs to address the growing compute demands in the vehicle, and enable our partners to move even faster, be more agile, and achieve a better total cost of ownership (TCO).

Supporting the new Arm AE IP, Arm and our partners are announcing a range of virtual platforms – some of which are available now – that are designed for specific vehicle functions. These off-the-shelf designs for virtual prototyping can be easily deployed by partners into vehicle development or customized for individual needs. This is alongside full stack software solutions from a broad range of automotive partners for a variety of SDV applications. This complete package of support makes it easier and faster for automotive engineers and developers to innovate and build computing solutions using the Arm AE IP portfolio without having to wait for the silicon to be in production, accelerating automotive development cycles by up to two years.

Optimized, scalable automotive computing for diverse use cases

Back in 2020, Arm launched the Cortex-A78AE and Cortex-A65AE CPUs. Both have been widely adopted across the automotive industry with over 25 active designs in flight. We have seen partners taking Cortex-A78AE into a wide range of automotive computing use cases, with the first of these now starting to hit vehicle mass production. This success has allowed Arm to engage with key partners to understand their desired next steps for future CPU designs.

It was clear from these discussions that our partners have growing demands for more compute and even higher levels of performance in the vehicle. This is alongside the need to deliver a faster time to market, better TCO and greater flexibility to enable them to reuse their software investments. With Arm Neoverse technology delivering on these requirements for the server market, we decided to bring a Neoverse CPU to the Arm AE IP product line through a brand-new CPU that has features purpose-built for automotive.

Arm Neoverse V3AE has been designed for use cases like high-end ADAS and autonomous driving that require the highest single-thread performance. Our engineering teams have added key AE features to the Neoverse V3 design, including transient fault protection (TFP) to enable use in applications targeting functional safety. Neoverse V3AE adopts the same underlying CPU performance and ISA that is deployed in the latest cloud and data center designs to address the growing compute demands in vehicles. This enables automotive partners to leverage cloud compute resources as part of their overall software validation, benefitting from having the same ISA in the cloud today as will be in the next generation of SDVs.

We are also launching two new Arm AE A-class CPUs, with different performance and power trade-offs for a variety of SDV use cases. The A-class CPUs and Neoverse V3AE are built on the Armv9-A architecture, which is another first for the automotive industry, so benefit from built-in security features and enhanced computing capabilities for a broad range of data types emerging in AI.

Arm Cortex-A720AE targets use cases like ADAS, Digital Cockpit and IVI that require a balance of higher performance with increased power efficiency. Our engineering teams have worked to add key AE features, like enhanced split-lock, optional TFP and enhanced software test libraries (STLs), to the “big” core Cortex-A720 CPU. Cortex-A720 is the “work horse” of many SoCs in the most widely used consumer devices, like smartphones, and brings a significant sustained performance uplift (which is higher performance within the same power budget) over the previous generation Cortex-A78AE. We have seen a 30 percent performance uplift when moving automotive relevant workloads from Cortex-A78AE to Cortex-A720AE on perception benchmarks, like point cloud transformation and birdseye construction. This follows work with our partners to establish what performance means for their key automotive workloads.

Arm Cortex-A520AE targets a variety of automotive use cases that are increasingly focused on processing compute workloads as efficiently as possible. This is particularly relevant for ADAS use cases where known vision processing requirements are now being optimized for lower power. The “LITTLE” core Cortex-A520AE plays a vital role, either in a heterogeneous SoC (which is mix of big and LITTLE cores) or as the primary processor, as it can achieve the big core workloads of previous CPU designs.

Pairing Cortex-A720AE with Cortex-A520AE in CPU cluster configurations through a new AE version of Arm’s DynamIQ Shared Unit (DSU-120AE) enables a wider range of more flexible, scalable heterogenous SoC designs. DSU-120AE enables up to 14 cores in a cluster and a mix of Cortex-A720AE and Cortex-A520AE pairs.

Automotive real-time computing

While application processors are often the headline for automotive SoCs, it is important for vehicle manufacturers to meet the safety and real-time computing requirements that are so critical for the automotive market.

For many years, Arm’s partners have been designing SoCs with a mix of application processors and real-time cores. These real-time cores are often available as separated safety islands, both to monitor the application processors and enable the SoC to perform real-time computing tasks, like communications, system management and vehicle actuation. Moreover, Arm Cortex-R52 and Cortex-R52+ have become the automotive industry standard for safety islands with over 20 designs in flight.

Today, we are announcing the next generation Arm Cortex-R82AE, which brings 64-bit computing to real time, safety processing for the very first time. Cortex-R82AE will enable more performant safety island designs that seamlessly integrate and interact with application processor cores, all in the 64-bit memory space. It also supports traditional real-time computing use cases and some rich operating system (OS) workloads.

Vehicle vision fit for the future

Camera-based ADAS systems have become widely adopted by various automotive manufacturers. From single camera AEB to multicamera L2+ ADAS, vision systems are making vehicles safer as they continue to add more autonomous driving features.

Arm has an extensive track record developing ISPs, with millions of vehicles on the road today using current generations of our ISP (Arm Mali-C71AE and Mali-C78AE). The latest ISP, the Arm Mali-C720AE, is the result of a long-term research project into the different use cases of vision systems broadly categorized as “human vision” and Computer Vision (CV). Human vision reflects camera systems that process images suited to a person’s viewing requirements, which often means vibrant and realistic colours, sharp edges and corrected pixel errors. However, CV algorithms process the input data entirely differently. This means that currently images are often processed separately either through different ISPs or serially reprogramming the ISP.

Mali-C720AE solves this challenge through enabling multiple parallel pipelines to be tuned differently across both human vision and CV use cases. This reduces the time taken to process images, speeding up the overall reaction time of the computing system. These multiple ISP pipelines also reduce memory usage, which saves SoC power and area.

Furthermore, Mali-C720AE provides the flexibility to add or remove processing blocks to balance area with image processing requirements for specific partner needs without compromising functional safety. Finally, the differentiable ISP model enables Arm’s automotive partners to tune image quality for CV-based applications faster, more cost-effectively and to a higher level of performance. The differentiable and accelerated ISP models will be available as standalone software products, enabling software development and image quality tuning before silicon is available for a quicker time to market.

Creating SoC solutions with System IP and open standards

Alongside the new CPUs and ISP added to the Arm AE IP portfolio, we are introducing new critical configurable system IP components to enable our partners to quickly and successfully design their SoCs. These include safety capable versions of our latest interconnect and GIC.

New classes of high core count automotive computing systems are required across ADAS, autonomous and Digital Cockpit use cases. Arm has added “AE” features to our Coherent Mesh Network for the Neoverse S3 (CMN S3AE) to enable enhanced functional safety features. CMN S3AE also supports core counts scaling beyond 64 core per chip and coherent multi-chip designs that can be implemented as chiplets.

Across the spectrum of automotive computing systems, safety capable Network on Chip (NoC) interconnects are often needed. We have added a range of safety features to our highly configurable NoC product (NI-710AE), so partners can build everything from complete safety microcontrollers (MCUs) to safety critical subsystems and safety islands in larger SoCs.

Multi-processor systems require the sharing of interrupts between cores to enable rich operating systems to manage resources and achieve virtualization. GIC-720AE brings the safety features outlined previously to our GIC IP, with these being aligned to the latest Arm AE CPU products.

Arm has always embraced open standards, as this enables a rich ecosystem of partners to thrive when using the Arm AE IP designs, while also enabling greater portability and software re-use. A great example is Arm’s partnership with Arteris where we have enabled Arteris to validate their own interconnect products (NCore and FlexNoc) using our latest CPU IP. More recently, Arm and Arteris have been validating combinations of CPUs and Arteris Ncore around the AMBA5 CHI.E standard. This validation work demonstrates to the ecosystem that they can be confident when choosing combinations of our IP to build their specific SoC solutions.

Enhanced safety and security

Safety and security are fundamental to automotive computing use cases. The two are interrelated as the device security can impact the safety of the computing system and, ultimately, the vehicle. As more vehicles become connected devices, the threat models evolve to become more like those commonly used against consumer devices. The challenge for the automotive industry is that malicious actors no longer need to have physical access to the vehicle to gain control and cause harm.

Arm is already at the forefront of mobile device security. Working closely with device manufacturers and major OS vendors, the Armv9-A architecture includes features to mitigate against memory safety violations, control flow hijack and buffer overflow attacks, which include Pointer Authentication and Branch Target Identification and Memory Tagging Extension. The new Arm AE CPUs bring these capabilities to the vehicles of the near future.

New emerging industry standards are defining how vehicles are developed and deployed. This not only includes the relevant security features, but also requirements for security risk management for the development, production, operation, maintenance and decommissioning of electronic and electrical (E/E) automotive systems. These ripple through to the supply chain, as vehicle manufacturers need to understand the security development process of all the products they and their suppliers use. We already have a robust process for our IP development and are delivering documentation to our partners to use in their security assessments to support them and the wider automotive supply chain.

Different use cases in the vehicle are evolving to require different functional safety capabilities. The Arm AE IP portfolio is providing a richer set of options to our partners, whether they are targeting ASIL B usage or full ASIL D capabilities for different processing elements in their SoC. Working with Arm’s complimentary software, which includes Software Test Libraries (STLs) and SystemReady, this enables a broad range of functional safety features and optimizes the performance, power and area (PPA) for the desired safety capability of the automotive computing system. Learn more about the Arm AE IP’s functional safety capabilities in this blog.

Learn how Arm’s AE technologies can address the challenges you’re facing with this customized, interactive manual.

Click to read The Automaker’s Glovebox ManualSetting the pace for the future of automotive computing

The additions to the Arm AE IP portfolio will power and enhance the next generation of vehicles. Working in close partnership across the entire automotive supply chain, including mobility service companies, new and traditional OEMs, Tier1s and silicon vendors, Arm is leveraging the latest technology innovations to create optimized products suited to core and evolving computing requirements across automotive markets.

From new and advanced AI-powered compute workloads and use cases in hardware and software to enhanced security and safety features, we are delivering the technology suite best placed to respond to the seismic transformation taking pace in the automotive industry. With this leading position, ongoing partner engagement and continued long term focus, the future of automotive computing is being built on Arm.

Arm Automotive Enhanced

Arm offers a broad range of Automotive Enhanced IP technologies.

Any re-use permitted for informational and non-commercial or personal use only.